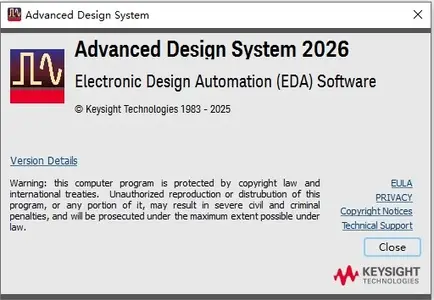

PathWave Advanced Design System (ADS) 2026 Update 0.1 | 3.4 Gb

Keysight is releasing Advanced Design System (ADS) 2026 Update 0.1, which includes several bug fixes to improve functionality, along with an updated licensing module from Advanced Design System (ADS) 2026.

Advanced Design System (ADS) 2026 introduces new capabilities for RF/MW, High-Speed Digital, Power, and Quantum Electronics applications, with powerful enhancements to 3DEM, layout verification, electro-thermal simulation, circuit simulation models, data and design management, and high-performance computing (HPC).

PathWave Advanced Design System (ADS) 2026 Update 0.1 Release Notes

ADS 2026 Update 0.1 includes several bug fixes to enhance functionality, along with an updated licensing module. ADS 2026 Update 0.1 replaces ADS 2026.

ADS 2026 Update 0.1 includes several bug fixes to enhance functionality, along with an updated licensing module. ADS 2026 Update 0.1 replaces ADS 2026.

Enhancements

Verification

Design Rule Checker

The following updates have been made to the DRC Dialog.

- DRC rule folder pulldown shows rule folders configured at the PDK level.

- DRC custom rule callbacks are loaded.

Fixed Issues

Data Display

General

- Fixed positioning equations with a thick outline.

- Fixed a potential crash in loading the data-display file with Python equations.

- Fixed the copy/paste of equations not immediately appearing in the Expression Manager.

Design & Tech Management

General

- Fixed the unreadable highlighted part search text for the dark mode theme.

- Fixed copy/paste of HSD components, losing hierarchical data.

- Fixed generating netlist in Python automation due to undefined function: deutil_get_path_one_dir_up.

- Fixed a potential problem with Python Exporter when the EDA chat option is installed.

Design Cloud

RF Microwave

- Simulations that consume encrypted models (Spectre models or Verilog-A models) are now supported on Design Cloud.

Note: For Verilog-A encrypted models, Design Cloud expects the encrypted Verilog-A file with the extension .vax

Design Editing and Layout

General

- The Materials file reader has been fixed to report syntactical errors in the materials database file.

- Some bondwires to Smart Mount instances were not connecting. This issue has now been fixed.

EM Simulation

EM Integration

- An issue in the LTD substrate importer has been fixed to properly deal with conductors named 'GATE' or 'DIFFUSION'.

FEM

- An issue in the FEM mesher has been fixed that caused layers to be skipped in the meshing process.

Momentum

- An issue has been fixed to apply the via model correctly. In specific setups, the 3D via model was enforced despite a different selection in the simulation setup.

- Warning messages have been updated to mention the 'Closed Loop' feed type rather than 'SMD'.

- An issue has been fixed in the 'Closed Loop' feed type in a microwave mode simulation that was causing incorrect results at lower frequencies.

- The 'Closed Loop' feed type algorithm has been refined to prevent feed lines from overlapping.

RFPro

- A bug in 'FEMizer' has been fixed to construct the impedance line of a waveguide port properly. Previously, in specific cases, you could get a (false) warning that the impedance line crossed 2 electrically isolated domains.

- FEM simulation data will now be reused in case the number of parallel jobs or the number of threads changed. Previously, there was no data reuse in that case.

- When launching RFPro from Cadence Virtuoso or Synopsys Custom Compiler, you could get a 'Keysight License Error' dialog, even though you have a valid license. That issue has been addressed.

- An issue has been addressed that prevented RFPro from starting in Synopsys Custom Compiler when the LOCALE setting is not UTF-8 compatible.

- An issue has been fixed in the Python 'exportFarFieldToFfio' function to export a far field to an .ffio file.

HSD

General

- Fixed a bug in the SnP component where it errored out when attempting to open after placing an empty S[0–99]P component first, followed by a new SnP component.

- Fixed a bug in the C-PHY Waveform Source where, if the Transient simulator's MaxTimeStep is too small, it can cause signal distortion

DDR/Memory

- Fixed a bug in the Memory Designer where a simulator limitation warning pop-up appeared when the user selected Statistical simulation mode first and then enabled Pathfinding mode.

- Fixed a bug in the Memory Designer where the package model ground was not connected to the global ground during the simulation when the Interconnect Model was used as the package model in the IBIS file.

- Fixed a bug in the Memory Designer where ADS crashed when using an EMD model and attempting to change the signal parsing method using the 'Assign signal property by' option.

- Fixed a bug in the Memory Designer where the CS (chip select): CLK (clock) ratio was set to 2:1 instead of 1:1 in the LPDDR6 transient simulation.

SerDes

- Fixed a bug in the System Designer for USB, where the USB simulation did not generate waveforms for compliance tests

- Fixed a bug in the System Designer for USB, where the USB simulation pattern was mapped to 4B3T instead of 11B7T

- Fixed a bug in the System Designer for USB, where the USB4 v4 compliance software tried to run the Preset test regardless of whether it was selected or not.

- Fixed a bug in the System Designer for Ethernet, where the Host and Module components were netlisted as USB components, causing the USB simulator license to be checked out instead of the Ethernet simulator license during simulation

- Fixed a bug in the System Designer for Ethernet where the VPI optical link (VOL) caused invalid simulation results in EOE(Electrical -Optical - Electrical) simulations.

Power Electronics

General

- Fixed the issues related to lib/cell name with upper letters and removed air-core in Transformer Designer.

Quantum

General

- A bug in the Momentum simulator, introduced in version 2026.00, has been fixed to properly deal with the perfect electric conductor (PEC) material specification. The bug caused inaccurate Q-factors for resonances.

PathWave Advanced Design System (ADS) provides a complete set of simulation technologies, ranging from frequency and time-domain circuit simulation to electromagnetic field simulation. ADS lets you fully characterize and optimize designs. The single, integrated design environment provides the system and circuit simulators, along with schematic capture, layout, and verification capability. ADS simplifies your design flow by eliminating the stops and starts associated with changing design tools in mid-cycle.

PathWave Advanced Design System (ADS)

This playlist comprises video tutorials focusing on ADS, providing valuable insights into various aspects, including front-to-back flow, schematic design, layout design, circuit simulation, EM simulation, and much more!

Keysight Technologies Inc. is the world's leading electronic measurement company, transforming today's measurement experience through innovations in wireless, modular, and software solutions. With its HP and Agilent legacy, Keysight delivers solutions in wireless communications, aerospace and defense and semiconductor markets with world-class platforms, software and consistent measurement science. The company's nearly 10,500 employees serve customers in more than 100 countries.

Owner: Keysight Technologies Inc.

Product Name: PathWave Advanced Design System (ADS)

Version: 2026 Update 0.1

Supported Architectures: x64

Website Home Page : www.keysight.com

Languages Supported: english

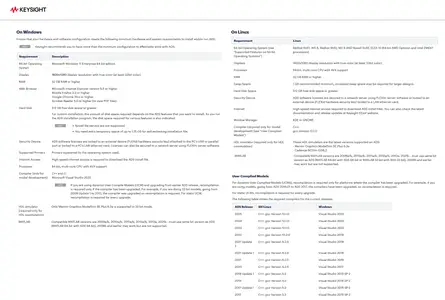

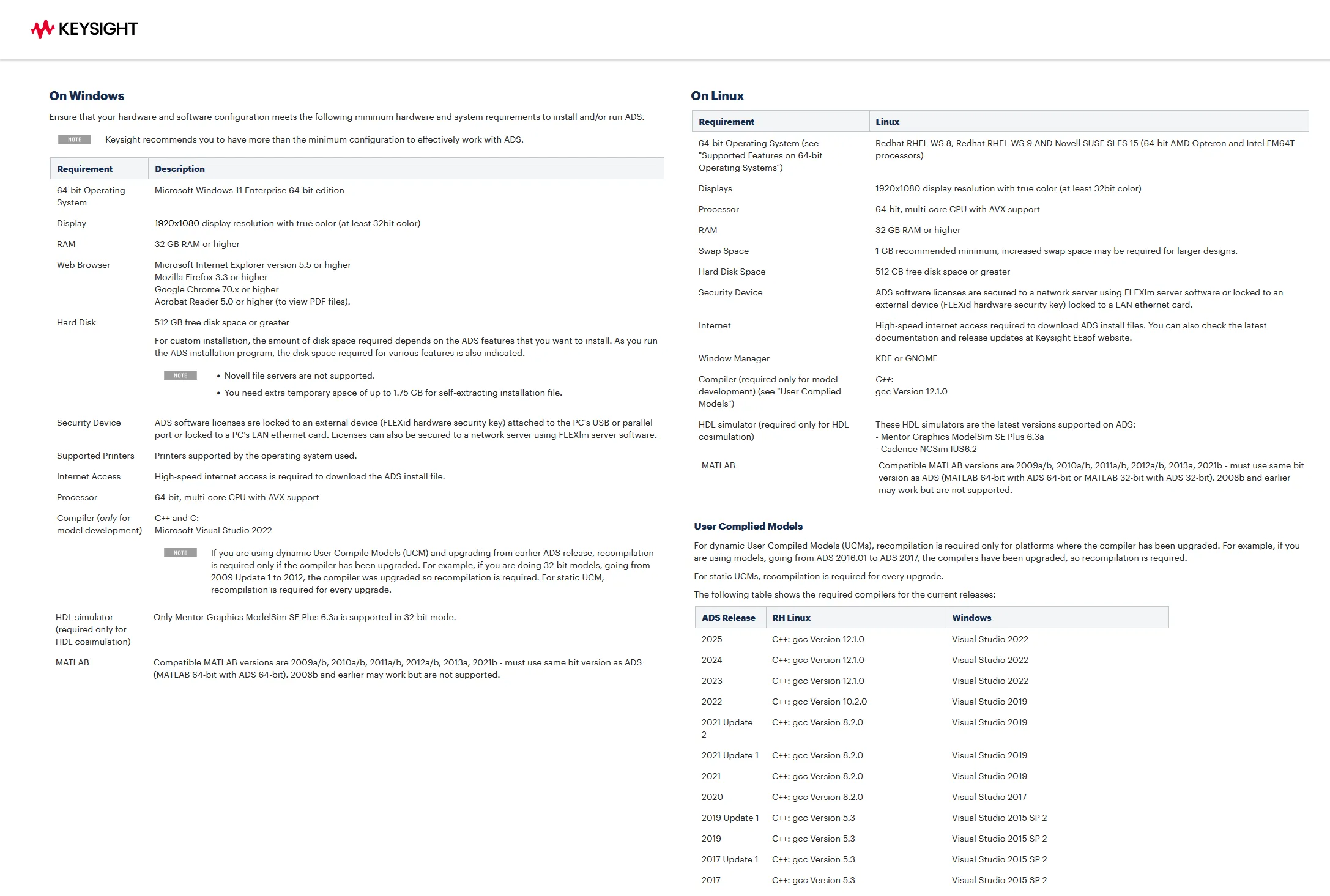

System Requirements: Windows *

Size: 3.4 Gb

Please visit my blog

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please

Added by 3% of the overall size of the archive of information for the restoration

No mirrors please